面向异构集成应用的 3D 系统封装玻璃面板嵌入设计与演示

引用

Ravichandran, S., Yamada, S., Ogawa, T., Shi, T., Liu, F., Smet, V., Sundaram, V., & Tummala, R. (2019)。面向异构集成应用的 3D 系统封装玻璃面板嵌入设计与演示。《微电子学与电子封装杂志》,16(3),124–135。 https://doi.org/10.4071/imaps.930748

关键词

- 玻璃面板嵌入 (GPE)

- 异构集成

- 3D 系统封装 (SiP)

- 晶圆级扇出 (WLFO)

- 玻璃通孔 (TGV)

- 芯片偏移

- 表面平坦度

- 重分布层 (RDL)

- 电气性能

- 可靠性

简介

本文介绍了一种基于玻璃面板嵌入 (GPE) 的 3D 封装技术,适用于高性能异构集成应用。这项新技术突破了现有技术的局限性,实现了高密度 I/O、卓越的电气性能以及大尺寸应用的潜力。

摘要

本文于 2019 年发表在《微电子学与电子封装杂志》上,介绍并演示了一种名为玻璃面板嵌入 (GPE) 的新型 3D 封装技术。这篇文章由 Siddharth Ravichandran、Shuhei Yamada、Tomonori Ogawa、Tailong Shi、Fuhan Liu、Vanessa Smet、Venky Sundaram 和 Rao Tummala 撰写,重点介绍了 GPE 革新电子设备异构集成的潜力。

以下是文章的概要:

- 由于对高性能和高能效的需求,电子行业需要先进的异构集成封装技术。

- 虽然晶圆级扇出型 (WLFO) 封装前景广阔,但由于其对环氧模塑料 (EMC) 的依赖,存在芯片偏移量大、表面粗糙和吸湿性等问题,限制了其在大尺寸应用中的使用。

- 相比之下,GPE 采用玻璃作为芯片嵌入的载体,与采用 EMC 的传统 WLFO 相比,具有诸多优势。GPE 具有以下优势:

1、卓越的电气性能:与 EMC 相比,玻璃在较高频率下损耗更低,因此非常适合高速应用。

2、增强设计灵活性:与中介层和硅桥不同,GPE 不受凸块限制,可实现类似硅片的重新布线,从而提高 I/O 密度并降低成本。

3、提升可靠性:GPE 中玻璃的可调整热膨胀系数 (CTE) 提高了可靠性,并允许直接进行电路板连接,这与基于 EMC 的封装不同。

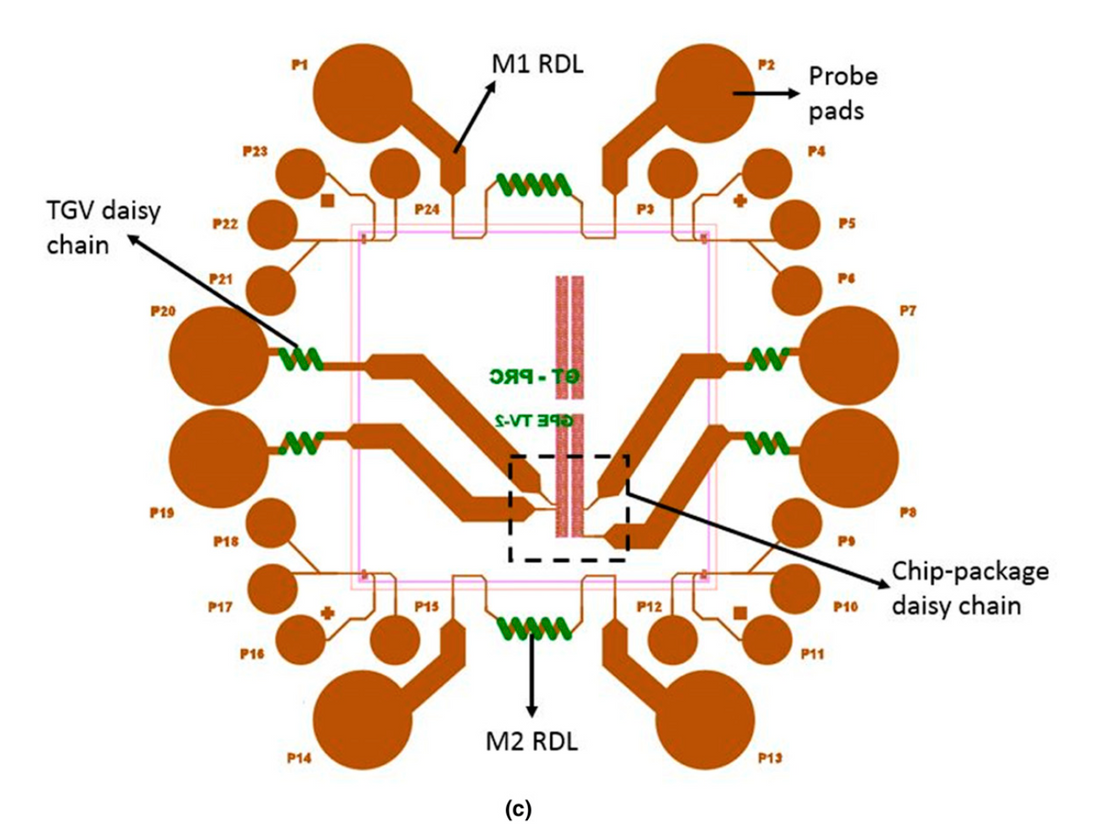

- 本文概述了 3D GPE 的制造工艺,并详细介绍了为克服传统 WLFO 中的芯片偏移和表面平面度问题等限制而实施的参数化工艺改进。这些改进包括:

1、通过使用芯片贴装膜 (DAF) 的新型芯片嵌入工艺,将芯片偏移最小化至 2 毫米以内。

2、通过优化电介质的层压和固化条件,实现小于 5 毫米的表面平面度。

3、使用通孔内通孔 (Via-in-Via) 方法,成功将直径 25 毫米、间距 300 毫米的玻璃通孔 (TGV) 集成到 250 毫米薄玻璃板上。该方法提高了良率、可靠性和电气性能。

- 本文最后强调,基于这些技术进步的 3D GPE 为异构集成提供了一种经济高效、高密度、高性能的解决方案。

来源:https://meridian.allenpress.com/jmep/article/16/3/124/420334/Design-and-Demonstration-of-Glass-Panel-Embedding